实时引线框架检测:FPGA与CPU处理架构对比

引线框架缺陷可能导致集成电路完全失效,造成高额生产损耗与退货成本。本文介绍一种高性能检测方案,将关键处理任务(如连通域分析和像素级并行计算)从CPU迁移至FPGA执行。通过破解CPU资源占用过高、系统稳定性不足及编程复杂度高等技术瓶颈,Basler基于FPGA的系统架构助力设备制造商构建新一代自动光学检测(AOI)系统,实现对微型化引线框架的更高速度与更高可靠性检测。

高速引线框架检测中的细节捕获

引线框架是半导体芯片与电路板间不可或缺的导电载体,其表面或尺寸缺陷(如毛刺、腐蚀、剥离或污染)均可能导致电性失效。对于AOI系统开发商而言,在检测速度持续提升、公差要求日益严苛的背景下,实现复杂引脚图案表面与几何缺陷的精准检测至关重要。

引线框架检测的核心技术挑战

现代引线框架检测需在精度、速度与系统稳定性间达成精密平衡:

规模化Blob分析:FPGA架构的先天优势

为满足高吞吐量需求,Blob分析需在单帧检测中实现数千根引脚的亚微米级精度分析。该过程需识别连通像素区域并提取尺寸、轮廓、位置等特征参数。

技术瓶颈:基于CPU的系统受限于软件开销与串行处理模式,难以高效稳定地执行大规模Blob分析。

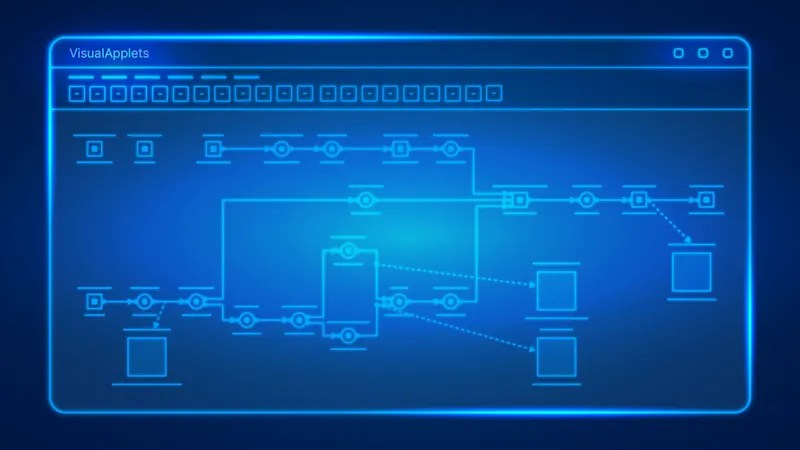

解决方案:FPGA架构支持真正的并行像素处理,可实现亚毫秒级延迟响应。将Blob分析任务卸载至FPGA执行,不仅显著降低CPU负载,更提升了检测可靠性。现代帧采集卡的FPGA芯片已突破传统预处理范畴,通过VisualApplets工具链,应用工程师无需深度硬件编码即可快速开发、部署及更新FPGA处理流程,实现开发效率与系统灵活性的双重提升。

跟Basler聊聊您的想法系统架构对比:FPGA vs. CPU

指标 | 基于FPGA的系统 | 基于CPU的系统 |

|---|---|---|

Blob 处理 | 并行像素流水线(100+ GPS/像素) | 基于线程的顺序分析 |

延迟 | 亚毫秒级光子到决策延迟 | 10–100毫秒(含OS/软件开销) |

能效 | 3.5–5 W(优化逻辑) | 15–30 W(通用计算) |

适配性 | 可重构支持新型Blob模式/缺陷 | 需软件更新/重新训练 |

引线架构检测结果对比:FPGA vs CPU系统

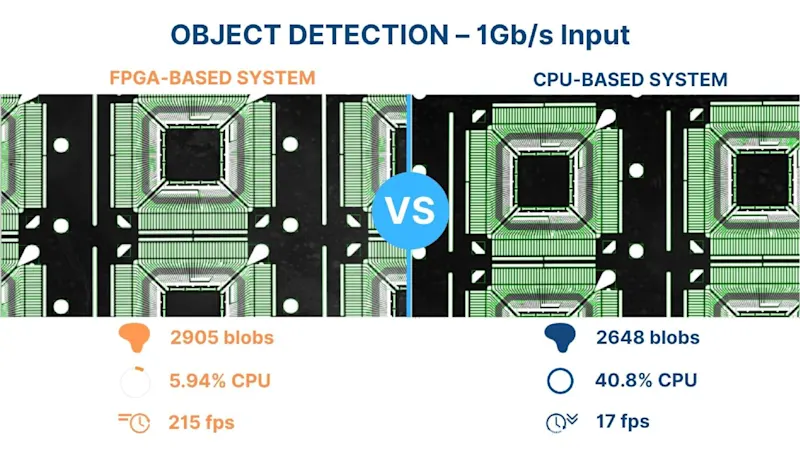

为验证FPGA与CPU架构在视觉处理中的实际性能差异,我们搭建了对比测试平台,平台设置:

• 相同配置:500万像素CXP-12接口相机(212fps,约1GB/s数据吞吐量)

• 相同环境:完全一致的PC硬件配置

• 相同对象:同一引线框架检测样本

基于FPGA的系统 | 基于CPU的系统 * | |

|---|---|---|

检测到的Blob数量 | 2905 | 2648 |

分辨率 | 5MP | 5MP |

速度 | 保持在 212 fps | 17 fps |

CPU 负载 | 5.94% | 40.8% |

*注:检测性能受软件算法优化程度影响。CPU系统更易出现丢帧现象,直接影响连通域数量统计、图像叠加显示及缺陷分类精度。

结论:基于FPGA的图像预处理实现数据源头级优化

FPGA视觉架构在高吞吐量、高精度引线框架检测中展现出显著优势:

硬件级数据处理:通过FPGA直接完成图像预处理,大幅降低CPU负载,突破软件处理瓶颈

系统稳定性提升:实测显示FPGA方案可减少90%以上的帧丢失率,确保检测流程连续性

检测精度保障:像素级并行处理能力使微小缺陷识别率提升3倍以上

对于AOI系统开发商而言,FPGA架构不仅带来性能跃升,更构建了可扩展的检测平台:

• 快速开发迭代:基于VisualApplets工具链,无需传统HDL编程即可实现FPGA逻辑部署与优化

• 适应工艺演进:灵活应对引线框架微型化、检测标准升级等需求变化

在当下封装工艺持续严苛化的产业趋势下,FPGA架构已不仅是性能增强方案,更是实现检测系统架构级革新的战略选择。

该解决方案所用的产品

想实施类似的解决方案?这些产品将能助您一臂之力。